垂直纳米环栅晶体管因其在减小标准单元面积、提升性能和改善寄生效应等方面具有优势,可满足功耗、中国科学院微电子研究所集成电路先导工艺研发中心研究员朱慧珑团队研发出p型具有自对准栅极的叠层垂直纳米环栅晶体管(IEEE Electron Device Letters,DOI: 10.1109/LED.2019.2954537,2019),并剖析n型器件。与p型器件制备工艺不同,n型器件在外延原位掺杂时,沟道和源漏界面处存在严重的杂质分凝与自掺杂问题。为此,团队开发出适用于垂直器件的替代栅工艺,利用假栅做掩模通过离子注入实现源漏的掺杂,既解决了上述外延原位掺杂难题,又突破了原位掺杂的固溶度极限,更利于对晶体管内部结构的优化和不同类型晶体管之间的集成。

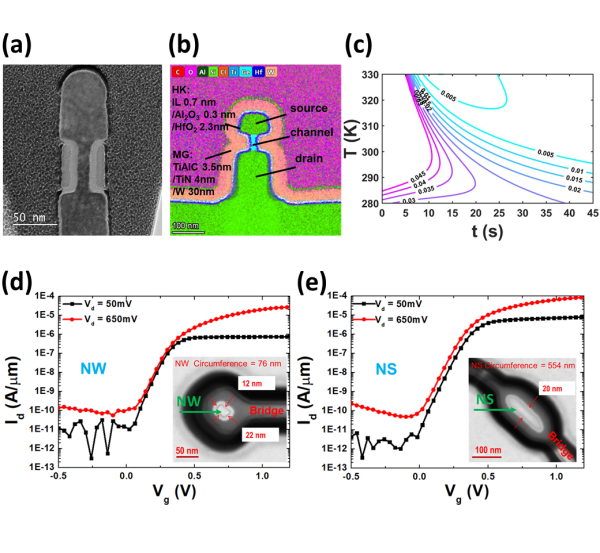

为获得可精确控制沟道和栅极尺寸的垂直环栅器件,选择性和各向同性的原子层刻蚀方法是关键工艺。科研团队对该方法开展了深入分析和研究,提出了相应的氧化—刻蚀模型,应用于实验设计,改进和优化了横向刻蚀工艺;用该刻蚀工艺与假栅工艺结合,制备出具有自对准栅的n型叠层垂直纳米环栅晶体管,器件栅长为48纳米,具有优异的短沟道控制能力和较高的电流开关比(Ion/Ioff),纳米线器件的亚阈值摆幅(SS)、漏致势垒降低(DIBL)和开关比为67 mV/dec、14 mV和3×105;纳米片器件的SS、DIBL和开关比为68 mV/dec、38 mV和1.3×106。

相关研究成果发表在Nano Letters(DOI:10.1021/acs.nanolett.1c01033)、ACS Applied Materials & Interfaces(DOI:10.1021/acsami.0c14018)上。研究得到中科院战略先导科技专项(先导预研项目“3-1纳米集成电路新器件与先导工艺”)、中科院青年创新促进会、国家自然科学基金等的资助。

(a)替代栅结构TEM截面,(b)垂直环栅纳米器件TEM截面的EDX元素分布图,(c)氧化-刻蚀模型,(d)n型垂直环栅纳米线器件的Id-Vg特性及TEM俯视插图,(e)n型垂直环栅纳米片器件的Id-Vg特性与TEM俯视插图。

内容来源:中国科学院

来源:中国科学院

原文链接:http://www.cas.cn/syky/202109/t20210915_4805820.shtml

版权声明:除非特别注明,本站所载内容来源于互联网、微信公众号等公开渠道,不代表本站观点,仅供参考、交流、公益传播之目的。转载的稿件版权归原作者或机构所有,如有侵权,请联系删除。

电话:(010)86409582

邮箱:kejie@scimall.org.cn