来源:中科院半导体所

中国科学院半导体研究所半导体超晶格国家重点实验室高速图像传感及信息处理课题组的刘力源研究员等研制出一款低功耗、高性能 Delta-Sigma调制器。相关研究成果以题目为 “A Discrete-Time AudioModulator Using Dynamic Amplifier With Speed Enhancement and Flicker Noise Reduction Techniques”的论文发表在集成电路芯片设计领域的顶级学术期刊IEEE Journal of Solid- State Circuits(JSSC)上。

Delta-Sigma调制器构成的模数转换器(ADC)广泛应用于高精度、低功耗物联网节点信号获取和处理场景,是目前模拟数字混合集成电路芯片设计研究领域的重要研究方向之一。在国家重点研发计划、国家科技重大专项和中国科学院青年创新促进会计划等项目支持下,课题组提出了一种新型动态放大器实现了开关电容积分器和两种闪烁噪声消除技术有效降低了噪声,研制出一种低功耗高精度离散时间Delta-Sigma调制器。

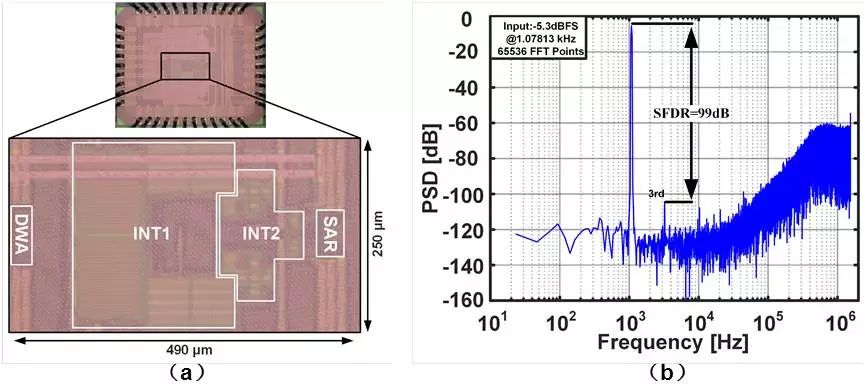

调制器采用运用四位逐次逼近量化器的两阶前馈架构,包括两个基于新型动态放大器的开关电容积分器和一个四比特逐次逼近量化器。积分器采用新型时序控制电路解决了电压跌落问题;采用加速支路在有效的共模电压范围内提高了积分器的差模特性;采用两种闪烁噪声抑制技术,改善了信噪比(SNR)。基于65nm CMOS工艺实现了调制器,测试结果表明,24kHz带宽内信号噪声失真比(SNDR)为89.6 dB,动态范围(DR)为91 dB,功耗仅为49μW @ 0.8 V电源电压。图1(a)和(b)分别为芯片照片和测量的输出信号频谱结果。论文第一作者为直博五年级学生马松。

论文下载地址:

https://ieeexplore.ieee.org/document/8862953

图1(a) 芯片照片 和 (b) 输出信号频谱

图1(a) 芯片照片 和 (b) 输出信号频谱

来源:bdtdsj 中科院半导体所

原文链接:http://mp.weixin.qq.com/s?__biz=MzI1OTExNzkzNw==&mid=2650450129&idx=1&sn=967316844d77fcffc25ad038e5471057&chksm=f273cecfc50447d920153b3e4f3485699d8c8a9846d4ea01f2ccff9883499013cc70f5f7cc4a&scene=27#wechat_redirect

版权声明:除非特别注明,本站所载内容来源于互联网、微信公众号等公开渠道,不代表本站观点,仅供参考、交流、公益传播之目的。转载的稿件版权归原作者或机构所有,如有侵权,请联系删除。

电话:(010)86409582

邮箱:kejie@scimall.org.cn