来源:高分子科学前沿

现代高性能应用于多功能电子设备逻辑、记忆器件都趋向于使用更小的晶体管尺寸和在更小的面积里堆叠更多的电路。然而,金属连接器维度的降低和堆叠密度的增加会导致电阻和电容延迟的增加,这将影响电子器件的运行速度。目前为止,研究者主要聚焦于降低于连接器的电阻,因为使用低温沉积工艺兼容金属氧化物半导体的互补的电介质集成具有大的技术挑战。连接器独立材料必须具有低的介电常数(κ),作为扩散屏障阻止金属迁移进半导体,并且其必须具有高的热、化学、机械稳定性。明确的,国际元件及系统技术蓝图提出在2028年之前发展介电常数低于2的低电介质。如氧化硅衍生物、有机化学物与空气胶等具有低介电常数的材料,都是大于2的,并且具有不稳定的的热、机械性质。在此,韩国蔚山科学技术院Hyeon Suk Shin联合三星综合技术院Hyeon-Jin Shin和英国剑桥大学Manish Chhowalla教授报道了一种3nm厚的无定型氮化硼薄膜,在100kHz和1MHz的工作频率下分别展示了1.78和1.16的超低介电性质。并且该薄膜展现了强的机械、高压稳定性。该项研究成果以题为“Ultralow-dielectric-constant amorphous boron nitride”发表在国际顶刊《Nature》上。 【图文解读】材料的制备与电镜表征:在这项工作中,研究者利用低温远程电感耦合等离子体-化学气相沉积(ICP-CVD)法在硅基底上获得了3nm厚的氮化硼薄层。透射电镜和选区电子衍射证明了其无定型的性质(命名为a-BN)。

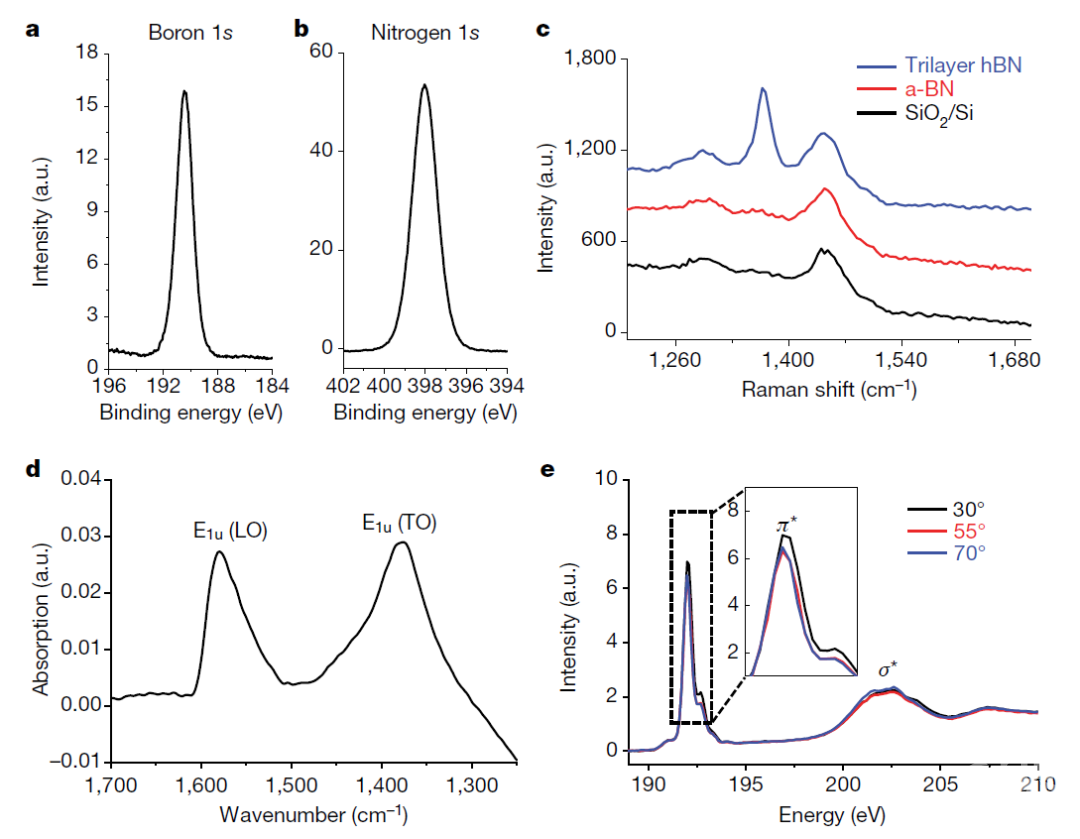

【图文解读】材料的制备与电镜表征:在这项工作中,研究者利用低温远程电感耦合等离子体-化学气相沉积(ICP-CVD)法在硅基底上获得了3nm厚的氮化硼薄层。透射电镜和选区电子衍射证明了其无定型的性质(命名为a-BN)。 图1. a-BN的原子结构。材料的化学成分表征:X射线光电子能谱数据分析得到其中B/N原子比例为1:1.08,表示了B和N是通过sp2键合的。拉曼谱图对比证明了其中没有六方晶系晶体信号。傅里叶红外测试确定了BN键的存在,而没有任何N-H或B-H的信号。另外,角相关近边X射线吸收测试探索了a-BN的精确化学和电子结构。

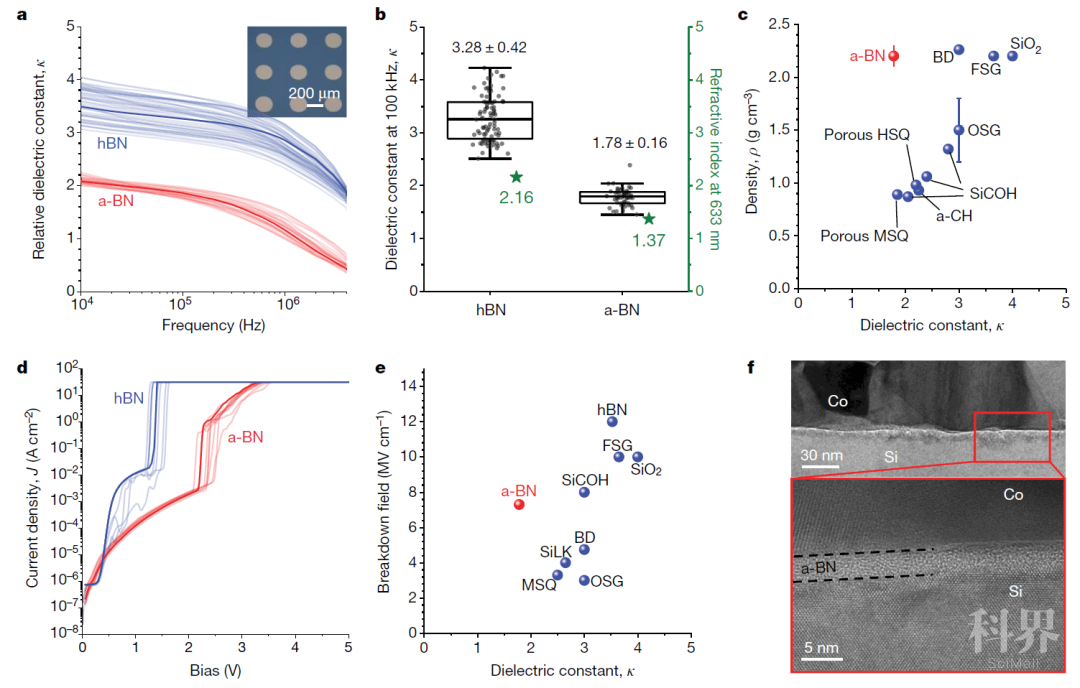

图1. a-BN的原子结构。材料的化学成分表征:X射线光电子能谱数据分析得到其中B/N原子比例为1:1.08,表示了B和N是通过sp2键合的。拉曼谱图对比证明了其中没有六方晶系晶体信号。傅里叶红外测试确定了BN键的存在,而没有任何N-H或B-H的信号。另外,角相关近边X射线吸收测试探索了a-BN的精确化学和电子结构。 图2. a-BN的化学结构。材料的介电性能:空气或真空的介电值为1,但由于固态物质会发生电极化,与电子器件的性能有着密切的关系。在100kHz测试下,a-BN的介电常数为1.78,而对比样六方晶型的hBN为3.28。在1MHz的频率测试下,a-BN更是降低到了1.16,非常接近于真空或空气的值。a-BN如此低的介电常数得益于BN间的非极性键和无序结构的构造,阻止了偶极的排列。低介电材料通常会做成多孔以利用空气的低介电性质,但这也降低了材料的密度,导致了较弱的机械强度。而对比一些著名的低介电材料,a-BN表现了最低的介电性质和最高的密度。研究者也测试了a-BN薄膜的机械强度,结果显示无论是硬度还是强度都比硅要强(>11GPa)。电击穿强度测试展示了a-BN具有超过两倍于hBN的强度,也是目前所报道介电常数低于2的材料的最高值。最后,研究者通过在a-BN上沉积80nm厚的钴膜,并在真空600℃下煅烧1h测试了a-BN的扩散势垒性质。在如此苛刻的条件下,既没有发生钴的扩散也没有硅化物的形成,表明a-BN可以同时作为低介电质和扩散屏障。

图2. a-BN的化学结构。材料的介电性能:空气或真空的介电值为1,但由于固态物质会发生电极化,与电子器件的性能有着密切的关系。在100kHz测试下,a-BN的介电常数为1.78,而对比样六方晶型的hBN为3.28。在1MHz的频率测试下,a-BN更是降低到了1.16,非常接近于真空或空气的值。a-BN如此低的介电常数得益于BN间的非极性键和无序结构的构造,阻止了偶极的排列。低介电材料通常会做成多孔以利用空气的低介电性质,但这也降低了材料的密度,导致了较弱的机械强度。而对比一些著名的低介电材料,a-BN表现了最低的介电性质和最高的密度。研究者也测试了a-BN薄膜的机械强度,结果显示无论是硬度还是强度都比硅要强(>11GPa)。电击穿强度测试展示了a-BN具有超过两倍于hBN的强度,也是目前所报道介电常数低于2的材料的最高值。最后,研究者通过在a-BN上沉积80nm厚的钴膜,并在真空600℃下煅烧1h测试了a-BN的扩散势垒性质。在如此苛刻的条件下,既没有发生钴的扩散也没有硅化物的形成,表明a-BN可以同时作为低介电质和扩散屏障。 图3. a-BN的介电性能。

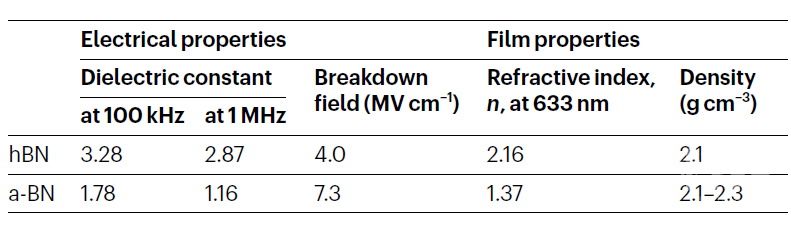

图3. a-BN的介电性能。 表1. a-BN和hBN的介电性质对比。总结:在这项工作中,研究者成功制备了一种3nm厚的无定型氮化硼薄膜,在100kHz和1MHz的工作频率下分别展示了1.78和1.16的超低介电性质,极度接近于空气和真空的介电值1,并且表现出了优异机械、高压稳定性。该工作成功证明了无定型氮化硼的低介电特点,并且用于高性能电子设备。

表1. a-BN和hBN的介电性质对比。总结:在这项工作中,研究者成功制备了一种3nm厚的无定型氮化硼薄膜,在100kHz和1MHz的工作频率下分别展示了1.78和1.16的超低介电性质,极度接近于空气和真空的介电值1,并且表现出了优异机械、高压稳定性。该工作成功证明了无定型氮化硼的低介电特点,并且用于高性能电子设备。来源:Polymer-science 高分子科学前沿

原文链接:https://mp.weixin.qq.com/s?__biz=MzA5NjM5NzA5OA==&mid=2651738208&idx=4&sn=73466ab56d9919702177f8ec28d7f501&chksm=8b4a4225bc3dcb33c8b4aa0b2084c496bb912b04eac1d510a5db1e639debe9b0ea80b41a4acc#rd

版权声明:除非特别注明,本站所载内容来源于互联网、微信公众号等公开渠道,不代表本站观点,仅供参考、交流、公益传播之目的。转载的稿件版权归原作者或机构所有,如有侵权,请联系删除。

电话:(010)86409582

邮箱:kejie@scimall.org.cn